AMD 6th Gen EPYC Venice: Sức Mạnh Vượt Trội Với Zen 6 và Zen 6C

AMD tiếp tục khẳng định vị thế dẫn đầu trong thị trường CPU dành cho máy chủ với dòng sản phẩm EPYC thế hệ thứ 6 "Venice", được xây dựng dựa trên kiến trúc Zen 6 và Zen 6C. Những thông tin rò rỉ mới nhất đã tiết lộ các chi tiết hấp dẫn về hiệu năng, cấu trúc và khả năng mở rộng của dòng CPU này, hứa hẹn mang đến một bước tiến vượt bậc trong lĩnh vực điện toán hiệu năng cao (HPC) và trung tâm dữ liệu.

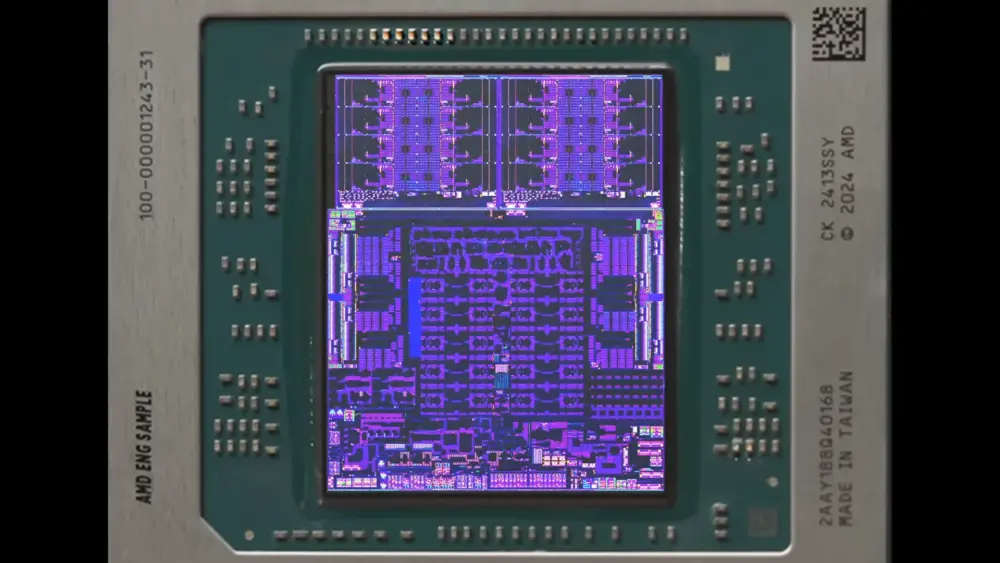

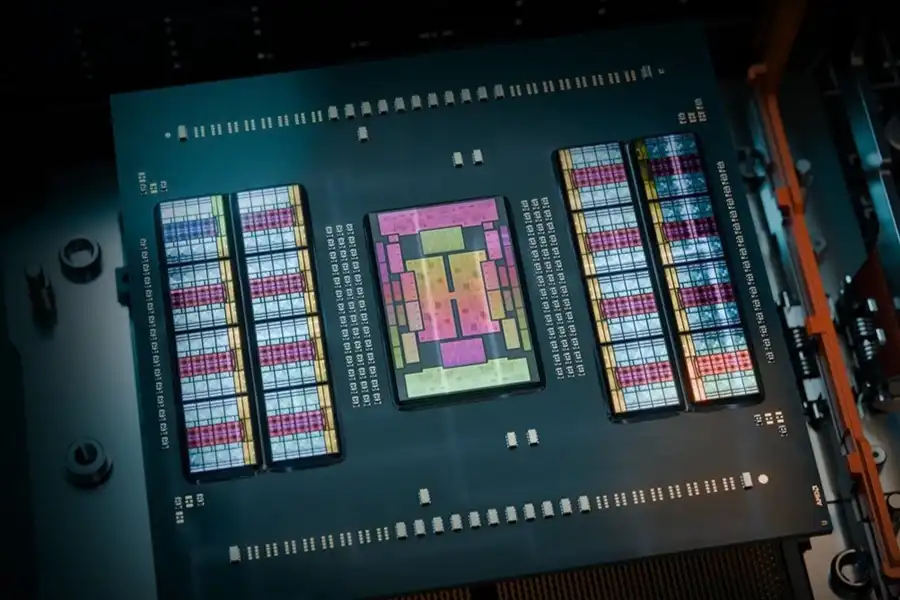

Cấu Trúc và Số Lượng Lõi Đỉnh Cao

Dòng EPYC 9006 Venice sẽ sử dụng tối đa 8 CCD (Core Complex Die), với hai biến thể chính:

-

Zen 6 (Classic): Cung cấp tối đa 96 lõi và 192 luồng, với mỗi CCD chứa 12 lõi. Đây là cấu hình hiệu năng cao, phù hợp cho các tác vụ đòi hỏi sức mạnh xử lý đơn luồng và đa luồng cân bằng.

-

Zen 6C (Dense): Đẩy giới hạn lên đến 256 lõi và 512 luồng, với mỗi CCD chứa tới 32 lõi. Biến thể này được tối ưu hóa cho các workload yêu cầu khả năng xử lý song song lớn, như ảo hóa, HPC, và các ứng dụng đám mây.

So với dòng EPYC 9005 Turin dựa trên Zen 5 (tối đa 128 lõi Zen 5 hoặc 192 lõi Zen 5C), Venice không chỉ tăng số lượng lõi mà còn giảm số lượng CCD (từ 16 xuống 8), giúp cải thiện hiệu quả và giảm độ phức tạp trong thiết kế chip.

Bộ Nhớ Cache L3 Khổng Lồ

Một điểm nổi bật của EPYC Venice là dung lượng cache L3 ấn tượng, lên đến 128MB cho mỗi CCD, tổng cộng 1GB cache L3 trên toàn bộ CPU 256 lõi mà không cần sử dụng công nghệ 3D V-Cache. So sánh với EPYC Turin (512MB L3 cho mẫu cao cấp nhất), Venice mang lại bước nhảy vọt về dung lượng cache, giúp tăng hiệu suất trong các ứng dụng nhạy cảm với độ trễ bộ nhớ. Với Zen 6C, mỗi lõi được phân bổ khoảng 2MB cache L3, đảm bảo hiệu quả xử lý cho các workload nhỏ và phân tán.

Công Suất và Nền Tảng Mới

AMD dự kiến giới thiệu hai socket mới cho dòng Venice:

-

SP7: Dành cho các CPU Zen 6C cao cấp với tối đa 256 lõi, có mức TDP khoảng 600W, tăng đáng kể so với 400W của Turin. Nền tảng này hướng đến các máy chủ high-end và HPC, hỗ trợ bộ nhớ DDR5 với 12 hoặc 16 kênh, mang lại băng thông bộ nhớ vượt trội.

-

SP8: Hỗ trợ CPU Zen 6 (96 lõi) và Zen 6C (128 lõi), với TDP dao động từ 350-400W, phù hợp cho các giải pháp scale-out và tiết kiệm chi phí.

Sự gia tăng TDP phản ánh nhu cầu về hiệu năng cao hơn, nhưng cũng đặt ra thách thức về làm mát. Các hệ thống sử dụng Venice có thể sẽ yêu cầu giải pháp làm mát chất lỏng trực tiếp (Direct Liquid Cooling) để duy trì hiệu suất ổn định, vì làm mát bằng không khí truyền thống khó đáp ứng.

Công Nghệ Sản Xuất 2nm Tiên Tiến

EPYC Venice sẽ là sản phẩm HPC đầu tiên được sản xuất trên tiến trình 2nm (N2) của TSMC, sử dụng công nghệ transistor nanosheet gate-all-around (GAA). So với tiến trình 3nm của Zen 5C, tiến trình 2nm hứa hẹn mang lại:

-

Hiệu suất tăng 15% ở cùng mức điện áp.

-

Tiết kiệm điện năng từ 24-35%.

-

Mật độ transistor tăng 1.15 lần, cho phép tích hợp nhiều lõi hơn trên cùng diện tích.

Sự kết hợp giữa kiến trúc Zen 6/Zen 6C và tiến trình 2nm không chỉ cải thiện hiệu năng mà còn tối ưu hóa hiệu suất trên mỗi watt, một yếu tố quan trọng trong các trung tâm dữ liệu hiện đại.

Nền Tảng và Kết Nối

Nền tảng SP7 và SP8 sẽ hỗ trợ các cải tiến đáng kể về I/O:

-

Bộ nhớ DDR5: Hỗ trợ 12 hoặc 16 kênh, với tốc độ lên đến DDR5-6400, cung cấp băng thông bộ nhớ lớn hơn để nuôi dưỡng số lượng lõi khổng lồ.

-

PCIe Gen 5 và Gen 6: Venice có thể cung cấp tới 128 làn PCIe Gen 5 và 64 làn PCIe Gen 6 (trong cấu hình SP7), đáp ứng nhu cầu kết nối tốc độ cao cho GPU, bộ nhớ NVMe, và các thiết bị mạng.

Ngoài ra, AMD có thể áp dụng các công nghệ đóng gói tiên tiến như silicon interposer (CoWoS-S) hoặc silicon bridge (InFO_LSI) để tăng cường kết nối giữa các CCD và IOD, giảm độ trễ và cải thiện hiệu suất tổng thể.

Ứng Dụng và Tầm Ảnh Hưởng

Với thiết kế tập trung vào khả năng song song hóa cao, EPYC Venice nhắm đến các ứng dụng như:

-

HPC: Xử lý các workload tính toán phức tạp trong nghiên cứu khoa học, mô phỏng, và trí tuệ nhân tạo.

-

Ảo hóa và đám mây: Hỗ trợ hàng trăm máy ảo trên một CPU duy nhất, tối ưu hóa chi phí và không gian rack.

-

Cơ sở dữ liệu lớn: Cache L3 khổng lồ và băng thông bộ nhớ cao giúp tăng tốc các truy vấn phức tạp.

Venice cũng là câu trả lời của AMD trước các dòng CPU Xeon thế hệ mới của Intel, như Diamond Rapids và Clearwater Forest, dự kiến ra mắt trong cùng khung thời gian (2026). Với số lượng lõi vượt trội và công nghệ sản xuất tiên tiến, AMD đang đặt mục tiêu duy trì lợi thế cạnh tranh trong phân khúc máy chủ.

Kết luận

Dòng CPU EPYC 9006 Venice với kiến trúc Zen 6 và Zen 6C đánh dấu một cột mốc quan trọng trong lộ trình phát triển của AMD. Với tối đa 256 lõi, 1GB cache L3, tiến trình 2nm, và các nền tảng SP7/SP8 mạnh mẽ, Venice hứa hẹn mang lại hiệu năng vượt trội, đáp ứng nhu cầu ngày càng tăng của các trung tâm dữ liệu hiện đại. Dù TDP cao và yêu cầu làm mát phức tạp có thể là thách thức, những cải tiến của Venice cho thấy AMD đang không ngừng đẩy giới hạn công nghệ CPU máy chủ.